Honolulu, Hawaii - June 16-20, 2024

Professor Xiaojin Zhao and postdoctoral researcher Dr. Haibiao Zuo from the College of Electronics and Information Engineering at Shenzhen University participated in the 44th IEEE Symposium on VLSI Technology and Circuits, held in Honolulu, Hawaii from June 16 to 20, 2024. Professor Zhao delivered a presentation titled "An In-Sensor PUF Featuring Optical Reconfigurability and Near-100% Hardware Reuse Ratio for Trustworthy Sensing" in the C13 session of the Symposium on VLSI Circuits. Dr. Haibiao Zuo served as the first author of the paper, with Professor Xiaojin Zhao as the corresponding author. Their research, supported by grants from the National Natural Science Foundation of China and the National Key R&D Program, represents a significant breakthrough for Shenzhen University and the National Key Laboratory of RF Heterogeneous Integration at the VLSI Symposium.

Professor Xiaojin Zhao delivers conference presentation at VLSI 2024.

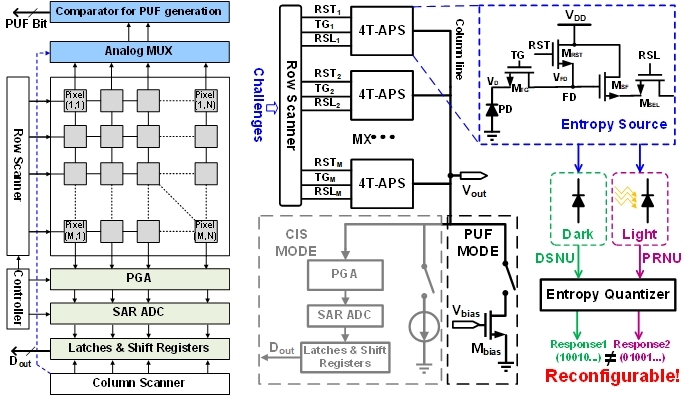

The paper addresses critical security threats faced by image sensors, such as demonstration attacks, virtual camera attacks, and image manipulation facilitated by Artificial Intelligence (AI) technologies. The paper introduces an innovative image sensor design featuring an optically reconfigurable Physically Unclonable Function (PUF) chip embedded within the image sensor. This PUF chip provides real-time encryption information to embed invisible watermarks, ensuring the traceability and reliability of image sensing. The paper proposes a dual-mode architecture for image sensors, combining "Optical PUF Entropy Source Extraction" and "Image Sensing" enabling the full reuse of the image sensor's 4T-APS pixel array with minimal additional hardware resources. The extraction of Physically Unclonable Function (PUF) output responses is facilitated solely by integrating mode-switching circuits on the column lines and a bias transistor.

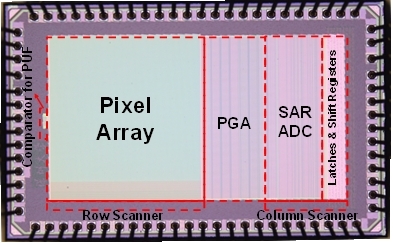

Furthermore, the fabrication of the first optical reconfigurable sensor-integrated PUF using a 65nm 1.2V standard CMOS process, featuring a 128×128 photo-sensitive pixel array. This PUF utilizes pixel Dark Signal Non-Uniformity (DSNU) and Pixel Response Non-Uniformity (PRNU) under uniform green light (550nm) to extract secondary entropy sources, enhancing the cryptographic strength of Challenge-Response Pairs (CRPs). The main features include: 1. Extremely high area efficiency of up to 1×10^36 bit/F^2 in PUF mode, with 99.735% silicon area reused for image sensors. 2. Optical reconfigurability based on PRNU, offering exponential and independent CRP spaces. 3. Strong resilience against various machine learning algorithm attacks, demonstrated through training with up to 40 million CRPs.

Trustworthy image sensor chip architecture and proposed in-sensor optical reconfigurable PUF.

Trustworthy image sensor chip micrograph

The VLSI Symposium, alongside ISSCC and IEDM, is among the premier conferences in the integrated circuits and semiconductor fields, attracting top research from international semiconductor industry and academia annually. Co-sponsored by the IEEE Solid-State Circuits Society, IEEE Electron Devices Society, and Japan Society of Applied Physics, the Symposium serves as a critical platform for showcasing and discussing cutting-edge technologies in integrated circuits and semiconductors.

The theme for the 2024 VLSI Symposium is "BRIDGING THE DIGITAL & PHYSICAL WORLDS with efficiency & intelligence," focusing on advanced VLSI technology development, innovative circuit designs, and applications in artificial intelligence, machine learning, Internet of Things, wearable/implantable biomedical devices, big data, cloud/edge computing, virtual reality (VR)/augmented reality (AR), robotics, and autonomous driving.

Attached: Conference link: https://www.vlsisymposium.org/